This article needs additional citations for. Unsourced material may be challenged and removed. (May 2017) () x86 assembly language is a family of, which provide some level of compatibility all the way back to the introduced in April 1972. X86 are used to produce object code for the class of processors. Like all assembly languages, it uses short to represent the fundamental instructions that the in a computer can understand and follow. Sometimes produce assembly code as an intermediate step when translating a high level program into. Regarded as a, assembly coding is and.

View Essay - programmation-en-assembleur-8086-pdf-february-10-2009-5-39-pm-170k from ECON 2 at Informatics Academy. Microprocesseur 8086 - TD 4 TD 4: Programmation. Download >>Download Jurnal penuaan dini.pdf Read. Cours programmation assembleur 8086 pdf. VTeam a Corporate Multipurpose Free Bootstrap.

Assembly languages are more typically used for detailed and time critical applications such as small or and. Contents • • • • • • • • • • • • • • • • • • • • • • • • • • • • History [ ] The and were the first CPUs to have an that is now commonly referred to as x86. These 16-bit CPUs were an evolution of the previous generation of 8-bit CPUs such as the, inheriting many characteristics and instructions, extended for the 16-bit era.

The 8086 and 8088 both used a 20-bit and 16-bit internal registers but while the 8086 had a 16-bit, the 8088, intended as a low cost option for embedded applications and small computers, had an 8-bit data bus. Further information: Each x86 assembly instruction is represented by a which, often combined with one or more operands, translates to one or more bytes called an; the instruction translates to 0x90, for instance and the instruction translates to 0xF4. There are potential with no documented mnemonic which different processors may interpret differently, making a program using them behave inconsistently or even generate an exception on some processors. These opcodes often turn up in code writing competitions as a way to make the code smaller, faster, more elegant or just show off the author's prowess. Syntax [ ] x86 assembly language has two main branches: syntax, originally used for documentation of the, and syntax.

Intel syntax is dominant in the and world, and AT&T syntax is dominant in the world, since Unix was created. Here is a summary of the main differences between Intel syntax and AT&T syntax: AT&T Intel Parameter order Source before the destination. Further information: x86 processors have a collection of registers available to be used as stores for binary data. Collectively the data and address registers are called the general registers.

Further information: The x86 processors support five modes of operation for x86 code, Real Mode, Protected Mode, Long Mode, Virtual 86 Mode, and System Management Mode, in which some instructions are available and others are not. A 16-bit subset of instructions are available on the 16-bit x86 processors, which are the 8086, 8088, 80186, 80188, and 80286. These instructions are available in real mode on all x86 processors, and in 16-bit protected mode ( onwards), additional instructions relating to protected mode are available. On the and later, 32-bit instructions (including later extensions) are also available in all modes, including real mode; on these CPUs, V86 mode and 32-bit protected mode are added, with additional instructions provided in these modes to manage their features. SMM, with some of its own special instructions, is available on some Intel i386SL, i486 and later CPUs.

Finally, in long mode (AMD onwards), 64-bit instructions, and more registers, are also available. The instruction set is similar in each mode but memory addressing and word size vary, requiring different programming strategies. The modes in which x86 code can be executed in are: • (16-bit) • (16-bit and 32-bit) • (64-bit) • (16-bit) • (16-bit) Switching modes [ ] The processor runs in real mode immediately after power on, so an, or other program, must explicitly switch to another mode if it wishes to run in anything but real mode. Switching modes is accomplished by modifying certain bits of the processor's after some preparation, and some additional setup may be required after the switch. Instruction types [ ] In general, the features of the modern are: • A compact encoding • Variable length and alignment independent (encoded as, as is all data in the x86 architecture) • Mainly one-address and two-address instructions, that is to say, the first is also the destination. • Memory operands as both source and destination are supported (frequently used to read/write stack elements addressed using small immediate offsets).

• Both general and implicit usage; although all seven (counting ebp) general registers in 32-bit mode, and all fifteen (counting rbp) general registers in 64-bit mode, can be freely used as or for addressing, most of them are also implicitly used by certain (more or less) special instructions; affected registers must therefore be temporarily preserved (normally stacked), if active during such instruction sequences. • Produces conditional flags implicitly through most integer instructions. • Supports various including immediate, offset, and scaled index but not PC-relative, except jumps (introduced as an improvement in the architecture). • Includes to a stack of registers. • Contains special support for atomic instructions ( xchg, cmpxchg/ cmpxchg8b, xadd, and integer instructions which combine with the lock prefix) • instructions (instructions which perform parallel simultaneous single instructions on many operands encoded in adjacent cells of wider registers).

Stack instructions [ ] The x86 architecture has hardware support for an execution stack mechanism. Instructions such as push, pop, call and ret are used with the properly set up stack to pass parameters, to allocate space for local data, and to save and restore call-return points. The ret size instruction is very useful for implementing space efficient (and fast) where the callee is responsible for reclaiming stack space occupied by parameters. When setting up a to hold local data of a there are several choices; the high level enter instruction (introduced with the 80386) takes a procedure-nesting-depth argument as well as a local size argument, and may be faster than more explicit manipulation of the registers (such as push bp; mov bp, sp; sub sp, size).

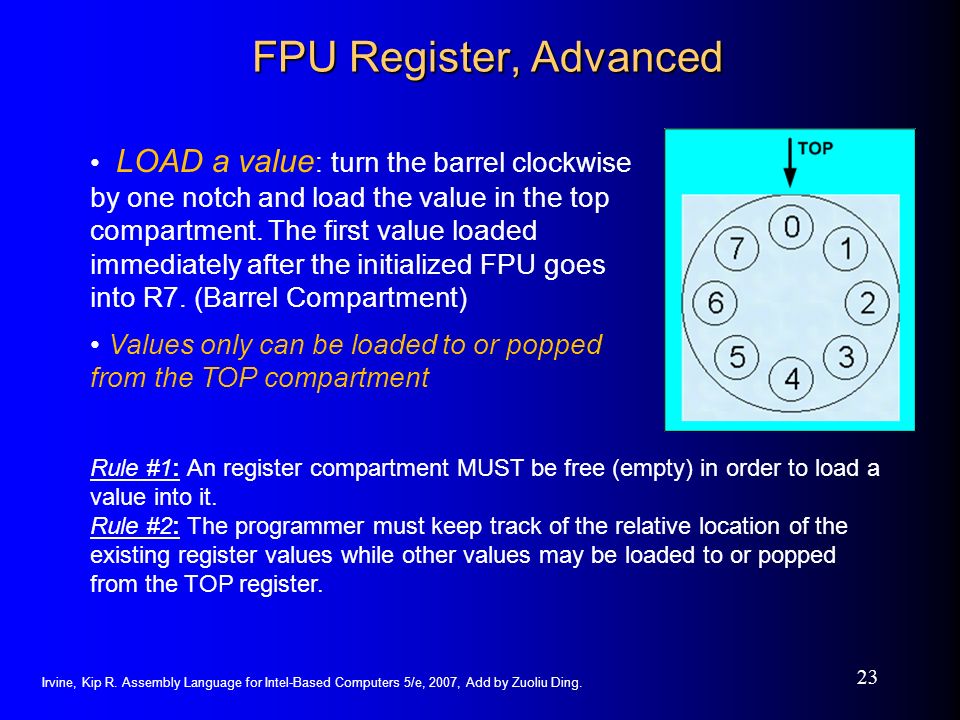

Whether it is faster or slower depends on the particular x86-processor implementation as well as the calling convention used by the compiler, programmer or particular program code; most x86 code is intended to run on x86-processors from several manufacturers and on different technological generations of processors, which implies highly varying and solutions as well as varying - and -level design choices. The full range of addressing modes (including immediate and base+offset) even for instructions such as push and pop, makes direct usage of the stack for, and data simple, as well as keeping the specifications and mechanisms relatively simple compared to some RISC architectures (require more explicit call stack details). Integer ALU instructions [ ] x86 assembly has the standard mathematical operations, add, sub, mul, with idiv; the and, or, xor, neg; arithmetic and logical, sal/ sar, shl/ shr; rotate with and without carry, rcl/ rcr, rol/ ror, a complement of arithmetic instructions, aaa, aad, daa and others. Floating-point instructions [ ] x86 assembly language includes instructions for a stack-based floating-point unit (FPU).

The FPU was an optional separate coprocessor for the 8086 through the 80386, it was an on-chip option for the 80486 series, and it is a standard feature in every Intel x86 CPU since the 80486, starting with the Pentium. The FPU instructions include addition, subtraction, negation, multiplication, division, remainder, square roots, integer truncation, fraction truncation, and scale by power of two. The operations also include conversion instructions, which can load or store a value from memory in any of the following formats: binary-coded decimal, 32-bit integer, 64-bit integer, 32-bit floating-point, 64-bit floating-point or 80-bit floating-point (upon loading, the value is converted to the currently used floating-point mode).

X86 also includes a number of transcendental functions, including sine, cosine, tangent, arctangent, exponentiation with the base 2 and logarithms to bases 2, 10,. The stack register to stack register format of the instructions is usually f op st, st( n) or f op st( n), st, where st is equivalent to st(0), and st( n) is one of the 8 stack registers ( st(0), st(1)., st(7)).

Like the integers, the first operand is both the first source operand and the destination operand. Fsubr and fdivr should be singled out as first swapping the source operands before performing the subtraction or division. The addition, subtraction, multiplication, division, store and comparison instructions include instruction modes that pop the top of the stack after their operation is complete. So, for example, faddp st(1), st performs the calculation st(1) = st(1) + st(0), then removes st(0) from the top of stack, thus making what was the result in st(1) the top of the stack in st(0). SIMD instructions [ ] Modern x86 CPUs contain instructions, which largely perform the same operation in parallel on many values encoded in a wide SIMD register.

Various instruction technologies support different operations on different register sets, but taken as complete whole (from to ) they include general computations on integer or floating point arithmetic (addition, subtraction, multiplication, shift, minimization, maximization, comparison, division or square root). So for example, paddw mm0, mm1 performs 4 parallel 16-bit (indicated by the w) integer adds (indicated by the padd) of mm0 values to mm1 and stores the result in mm0. Or SSE also includes a floating point mode in which only the very first value of the registers is actually modified (expanded in ). Some other unusual instructions have been added including a (used for in, such as is done in ) and a 16-bit multiply accumulation instruction (useful for software-based alpha-blending and ). SSE (since ) and extensions include addition and subtraction instructions for treating paired floating point values like complex numbers. These instruction sets also include numerous fixed sub-word instructions for shuffling, inserting and extracting the values around within the registers.

In addition there are instructions for moving data between the integer registers and XMM (used in SSE)/FPU (used in MMX) registers. Data manipulation instructions [ ] The x86 processor also includes complex addressing modes for addressing memory with an immediate offset, a register, a register with an offset, a scaled register with or without an offset, and a register with an optional offset and another scaled register. So for example, one can encode mov eax, [Table + ebx + esi*4] as a single instruction which loads 32 bits of data from the address computed as (Table + ebx + esi * 4) offset from the ds selector, and stores it to the eax register. In general x86 processors can load and use memory matched to the size of any register it is operating on. (The SIMD instructions also include half-load instructions.) The x86 instruction set includes string load, store, move, scan and compare instructions ( lods, stos, movs, scas and cmps) which perform each operation to a specified size ( b for 8-bit byte, w for 16-bit word, d for 32-bit double word) then increments/decrements (depending on DF, direction flag) the implicit address register ( si for lods, di for stos and scas, and both for movs and cmps).

For the load, store and scan operations, the implicit target/source/comparison register is in the al, ax or eax register (depending on size). The implicit segment registers used are ds for si and es for di.

The cx or ecx register is used as a decrementing counter, and the operation stops when the counter reaches zero or (for scans and comparisons) when inequality is detected. The stack is implemented with an implicitly decrementing (push) and incrementing (pop) stack pointer. In 16-bit mode, this implicit stack pointer is addressed as SS:[SP], in 32-bit mode it is SS:[ESP], and in 64-bit mode it is [RSP]. The stack pointer actually points to the last value that was stored, under the assumption that its size will match the operating mode of the processor (i.e., 16, 32, or 64 bits) to match the default width of the push/ pop/ call/ ret instructions. Also included are the instructions enter and leave which reserve and remove data from the top of the stack while setting up a stack frame pointer in bp/ ebp/ rbp.

However, direct setting, or addition and subtraction to the sp/ esp/ rsp register is also supported, so the enter/ leave instructions are generally unnecessary. This code in the beginning of a function. Push ebp; save calling function's stack frame (ebp) mov ebp, esp; make a new stack frame on top of our caller's stack sub esp, 4; allocate 4 bytes of stack space for this function's local variables.is functionally equivalent to just: enter 4, 0 Other instructions for manipulating the stack include pushf/ popf for storing and retrieving the (E)FLAGS register. The pusha/ popa instructions will store and retrieve the entire integer register state to and from the stack. Values for a SIMD load or store are assumed to be packed in adjacent positions for the SIMD register and will align them in sequential little-endian order. Some SSE load and store instructions require 16-byte alignment to function properly.

The SIMD instruction sets also include 'prefetch' instructions which perform the load but do not target any register, used for cache loading. The SSE instruction sets also include non-temporal store instructions which will perform stores straight to memory without performing a cache allocate if the destination is not already cached (otherwise it will behave like a regular store.) Most generic integer and floating point (but no SIMD) instructions can use one parameter as a complex address as the second source parameter. Integer instructions can also accept one memory parameter as a destination operand. Program flow [ ] The x86 assembly has an unconditional jump operation,, which can take an immediate address, a register or an indirect address as a parameter (note that most RISC processors only support a link register or short immediate displacement for jumping). Also supported are several conditional jumps, including jz (jump on zero), jnz (jump on non-zero), jg (jump on greater than, signed), jl (jump on less than, signed), ja (jump on above/greater than, unsigned), jb (jump on below/less than, unsigned).

These conditional operations are based on the state of specific bits in the register. Many arithmetic and logic operations set, clear or complement these flags depending on their result.

The comparison cmp (compare) and instructions set the flags as if they had performed a subtraction or a bitwise AND operation, respectively, without altering the values of the operands. There are also instructions such as clc (clear carry flag) and cmc (complement carry flag) which work on the flags directly. Floating point comparisons are performed via fcom or ficom instructions which eventually have to be converted to integer flags. Each jump operation has three different forms, depending on the size of the operand. A short jump uses an 8-bit signed operand, which is a relative offset from the current instruction. A near jump is similar to a short jump but uses a 16-bit signed operand (in real or protected mode) or a 32-bit signed operand (in 32-bit protected mode only). A far jump is one that uses the full segment base:offset value as an absolute address.

There are also indirect and indexed forms of each of these. In addition to the simple jump operations, there are the call (call a subroutine) and ret (return from subroutine) instructions. Before transferring control to the subroutine, call pushes the segment offset address of the instruction following the call onto the stack; ret pops this value off the stack, and jumps to it, effectively returning the flow of control to that part of the program. In the case of a far call, the segment base is pushed following the offset; far ret pops the offset and then the segment base to return. There are also two similar instructions, (), which saves the current register value on the stack, then performs a far call, except that instead of an address, it uses an interrupt vector, an index into a table of interrupt handler addresses. Typically, the interrupt handler saves all other CPU registers it uses, unless they are used to return the result of an operation to the calling program (in software called interrupts). How To Install A New Module In Joomla on this page.

The matching return from interrupt instruction is iret, which restores the flags after returning. Soft Interrupts of the type described above are used by some operating systems for system calls, and can also be used in debugging hard interrupt handlers. Hard interrupts are triggered by external hardware events, and must preserve all register values as the state of the currently executing program is unknown. In Protected Mode, interrupts may be set up by the OS to trigger a task switch, which will automatically save all registers of the active task.

Examples [ ]. Image base = 0x00400000%define RVA(x) (x-0x00400000) section.text push dword hello call dword [ printf ] push byte + 0 call dword [ exit ] ret section.data hello db 'Hello world!' Section.idata dd RVA ( msvcrt_LookupTable ) dd - 1 dd 0 dd RVA ( msvcrt_string ) dd RVA ( msvcrt_imports ) times 5 dd 0; ends the descriptor table msvcrt_string dd 'msvcrt.dll', 0 msvcrt_LookupTable: dd RVA ( msvcrt_printf ) dd RVA ( msvcrt_exit ) dd 0 msvcrt_imports: printf dd RVA ( msvcrt_printf ) exit dd RVA ( msvcrt_exit ) dd 0 msvcrt_printf: dw 1 dw 'printf', 0 msvcrt_exit: dw 2 dw 'exit', 0 dd 0 'Hello world!' Program for Linux in NASM style assembly [ ]. This program runs in 32-bit protected mode.; build: nasm -f elf -F stabs name.asm; link: ld -o name name.o;; In 64-bit long mode you can use 64-bit registers (e.g. Rax instead of eax, rbx instead of ebx, etc.); Also change '-f elf ' for '-f elf64' in build command.; section.data; section for initialized data str: db 'Hello world!' This program runs in 32-bit protected mode.; gcc links the standard-C library by default; build: nasm -f elf -F stabs name.asm; link: gcc -o name name.o;; In 64-bit long mode you can use 64-bit registers (e.g.

Rax instead of eax, rbx instead of ebx, etc.); Also change '-f elf ' for '-f elf64' in build command.; global main;main must be defined as it being compiled against the C-Standard Library extern printf;declares use of external symbol as printf is declared in a different object-module.;Linker resolves this symbol later. Segment.data;section for initialized data string db 'Hello world!' , 0Ah, 0h;message string with new-line char (10 decimal) and the NULL terminator;string now refers to the starting address at which 'Hello, World' is stored. Segment.text main: push string;push the address of first character of string onto stack.

This will be argument to printf call printf;calls printf add esp, 4;advances stack-pointer by 4 flushing out the pushed string argument ret;return 'Hello world!' Program for 64-bit mode Linux in NASM style assembly [ ]. BITS 64 SECTION.data Hello: db 'Hello world!' , 10 len_Hello: equ $ - Hello SECTION.text global _start _start: mov rax, 1; write syscall (x86_64) mov rdi, 1; fd = stdout mov rsi, Hello; *buf = Hello mov rdx, len_Hello; count = len_Hello syscall mov rax, 60; exit syscall (x86_64) mov rdi, 0; status = 0 (exit normally) syscall Using the flags register [ ] Flags are heavily used for comparisons in the x86 architecture. When a comparison is made between two data, the CPU sets the relevant flag or flags. Following this, conditional jump instructions can be used to check the flags and branch to code that should run, e.g.. Cli The flags register can also be directly accessed.

The low 8 bits of the flag register can be loaded into ah using the lahf instruction. The entire flags register can also be moved on and off the stack using the instructions pushf, popf, int (including into) and iret. Using the instruction pointer register [ ] The is called ip in 16-bit mode, eip in 32-bit mode, and rip in 64-bit mode.

The instruction pointer register points to the memory address which the processor will next attempt to execute; it cannot be directly accessed in 16-bit or 32-bit mode, but a sequence like the following can be written to put the address of next_line into eax.